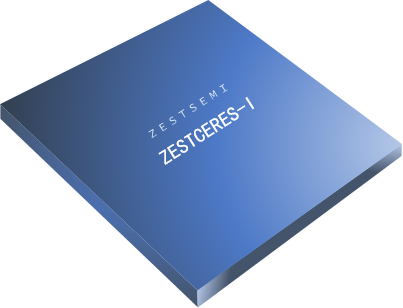

片上资源

片上资源

型号 | ZESTCERES-I | ZESTCERES-II | |

逻辑 | 逻辑单元 | 6000 | 12800 |

触发器 | 7500 | 16000 | |

存储 | 分布式存储(KB) | 70 | 171 |

36KB 块存储 | 5 | 20 | |

块存储总量(KB) | 180 | 720 | |

时钟 | 时钟管理单元(1MMCM+1PLL) | 2 | 3 |

I/O | 单端I/O | 100 | 150 |

差分I/O对 | 48 | 72 | |

PCIe(Gen2x4) | / | 2 | |

IP | DSP(25位x18位) | 10 | 40 |

AES加密模块 | / | 1 | |

ADC(12位1MSPS) | / | 1 | |

其它 | 温度 | 0°C至85°C | 0°C至85°C |

封装 | FTGB196 | CPG238 |

性能指标

性能指标

型号 | ZESTCERES-I | ZESTCERES-II | |

性能 | DSP(GHz | 1.25 | 1.25 |

BRAM(MHz) | 330 | 330 | |

| LVDS(Mb/s) | 1250 | 1250 | |

| DDR3(Mb/s) | / | 800 | |

SERDES(Gb/s) | / | 6.6 |

开发环境

开发环境

兼容业界主流开发工具,自研性能优化EDA工具,相同片上资源,提升性能>50%。